LEARN BY DOING CAL POLY College of Engineering

# Motivation

### The Computing Challenge

- Fundamental physical limitations

- Increasingly specialized hardware needed for continued performance scaling.

### **Open-Source Hardware**

- Hardware is entering an open-source renaissance (ISAs, CAD tools, processors, and libraries).

- Lack of support for advanced hardware techniques

- Ad hoc hardware development to date

#### Need for a flexible, unifying hardware development framework for emerging computing applications.

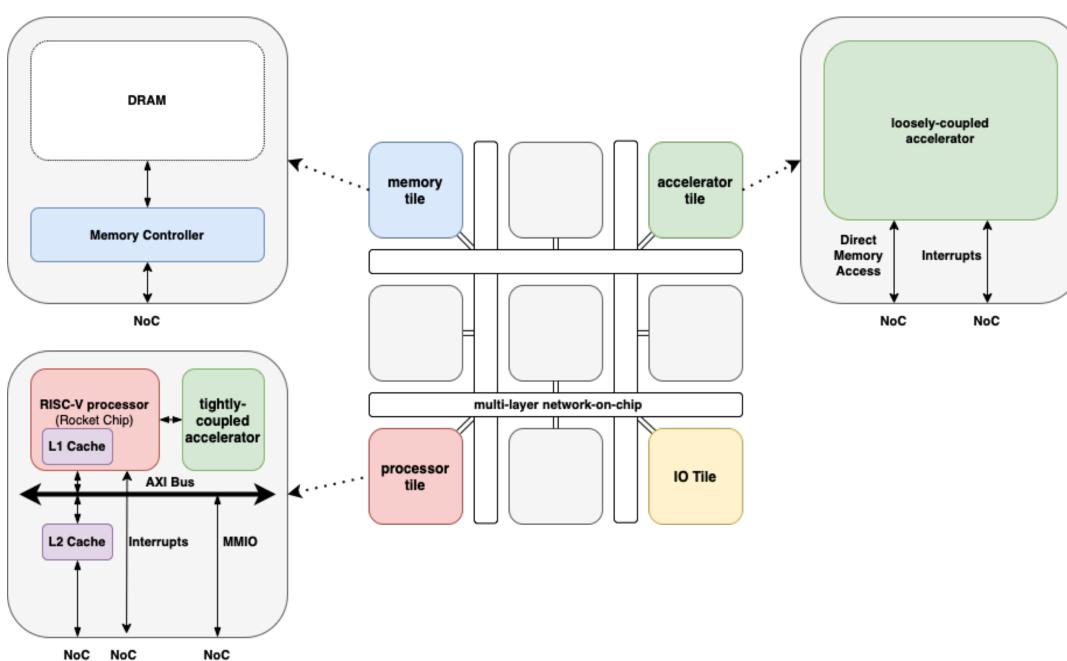

# **RAMP Framework**

The RAMP framework allows for rapid development of customtailored Systems-On-Chip, leveraging modern open-source tools.

An open-source System-on-Chip design framework, surrounding modular processor, memory, IO and accelerators.

# Hardware Goals

#### **Advanced Techniques**

- Energy Efficiency

- Full System

### Targets

- FPGA with DRAM

- AWS Cloud Instance

- VLSI tools

### Extendibility

- Modular Design

- Integrated Testing

- Formal Methods

# A Flexible Computer Architecture and Tools for CENG Computing Projects Curtis Bucher, Joseph Callenes Computer Engineering

# **RAMP CORE**

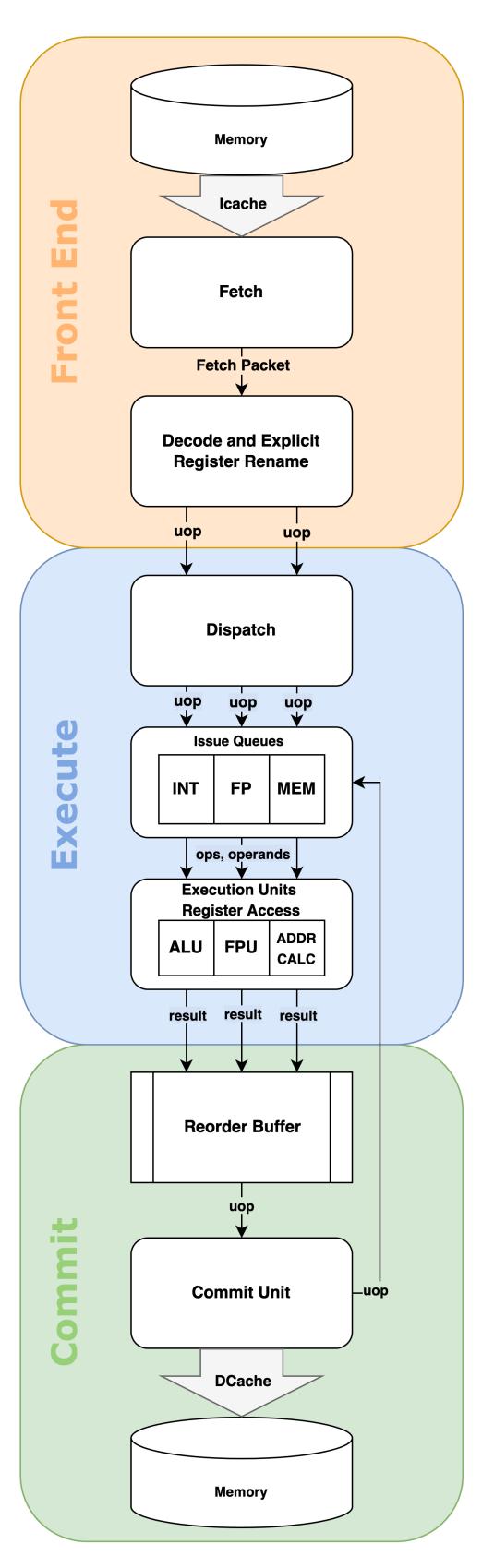

RAMP Core's out-of-order, superscalar design allows for multiple instructions to be executed simultaneously, greatly increasing performance.

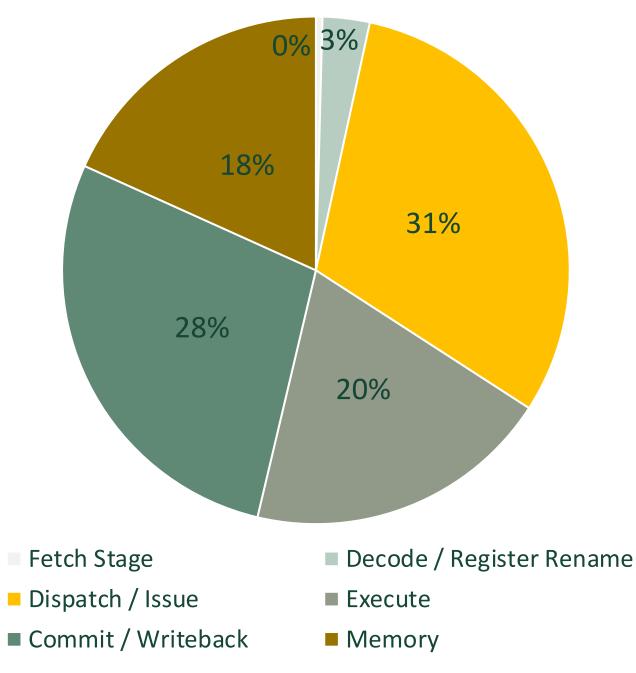

## Ramp Utilization by Stage

# **RAMP RISC-V Superscalar Processor**

- First OoO RISC-V processor to use PyMTL3

# Pipeline Multi-Iss Dynam

Scheduli Branch Predictio

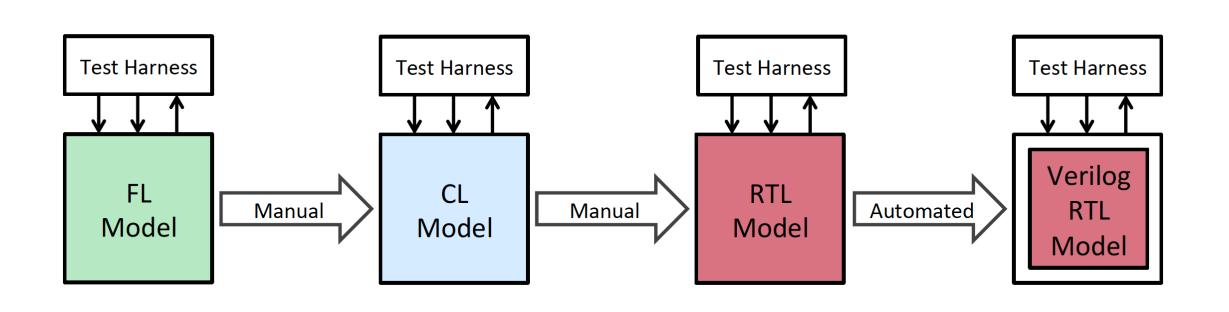

# PyMTL3

- An open-source Python framework for hardware modelling, generation, simulation and verification.

- Multi-level development paradigm lowers barrier to entry for non-specialists, and allows for more rapid development and

- experimentation

## **Python Packages**

- Python base will introduce tools previously detached from hardware research. jupyter, pytest, hypothesis, numpy

## Verilator

- simulation and testing solution. testing.

- Powerful, lightweight open-source Verilog • Tightly integrated with PyMTL3 for unit

• An open-source, out-of-order (OoO) RV32I processor, for use in the RAMP framework.

• Leverages advanced hardware techniques.

|           | RAMP<br>CORE | OTTER<br>Pipelined | OTTER<br>Multicycle |

|-----------|--------------|--------------------|---------------------|

| ed        | Yes          | Yes                | No                  |

| sue       | Yes          | No                 | No                  |

| ic<br>ing | Yes          | No                 | No                  |

| n<br>on   | Yes          | No                 | No                  |

# **Open-Source Hardware Tools**

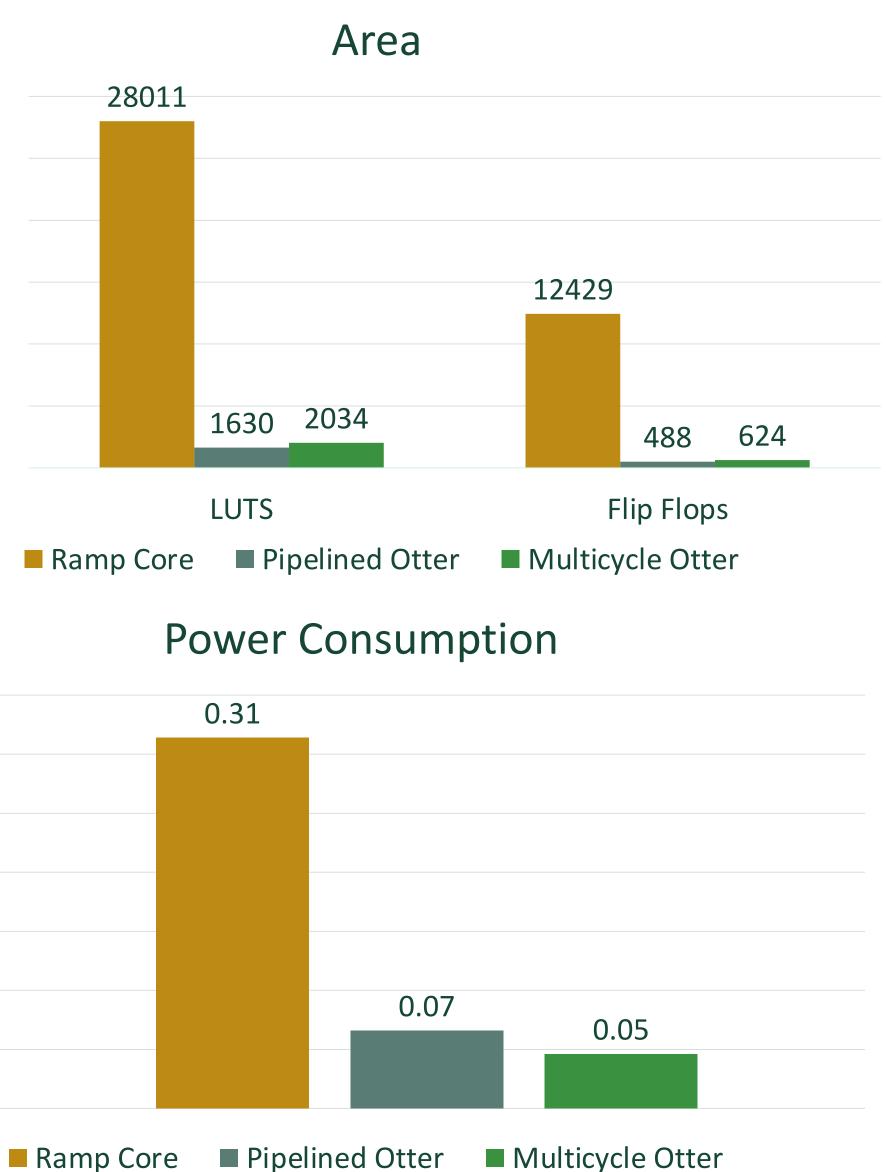

**6x** increase in power over Pipelined OTTER. Within embedded/IoT power-budget (<1W). Optimizing area and power subject for future work

## Summary

- solutions.

0.35

0.3

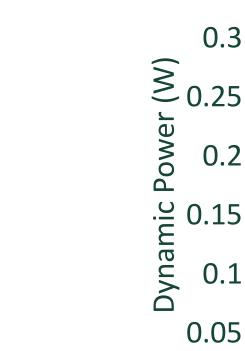

RAMP Core provides a **3x** speedup over Pipelined OTTER and over a **5x** speedup over Multicycle OTTER running bare metal benchmarks.

• RAMP Core outperforms all of Cal Poly's current processors in bare-metal benchmarks, provides researchers access to more advanced hardware techniques.

• RAMP Core's extendible, configurable design and centralized repository provide a robust framework for future education and research into modern computing